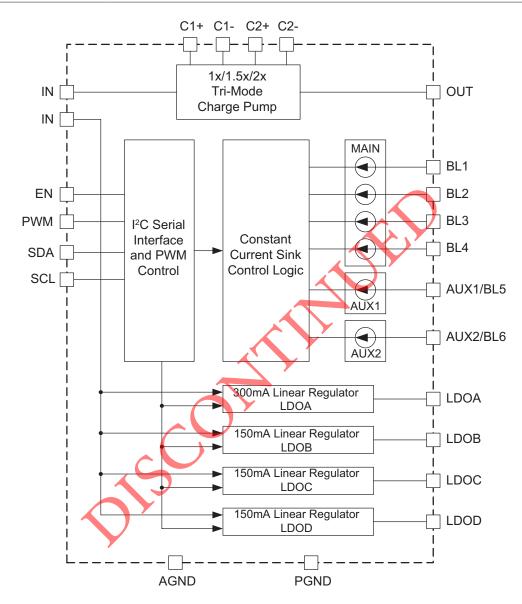

#### **General Description**

The AAT2863 is a highly integrated charge pump-based lighting management unit with four linear regulators optimized for single-cell lithium-ion/polymer systems. The charge pump provides power for all LED outputs and multiple LED configurations are available. The LED control current sinks can be programmed up to 30mA each and the two AUX LED outputs can be programmed up to 60mA each.

An I²C serial digital interface is used to enable, disable, and set the LED current to one of 32 levels. In addition the 6 LED channels, including two AUX channels, can be configured between MAIN/SUB. High power auxiliary channels' current matching is better than 5% for matched LED color and brightness. A separate PWM input allows the LED current sinks to be modulated at high frequencies as required by CABC or Dynamic backlight power saving schemes.

The AAT2863 also provides four high-performance lownoise MicroPower<sup>TM</sup> low dropout (LDO) linear regulators. The regulators are enabled and their output voltages are I²C programmable. One MicroPower<sup>TM</sup> LDO has a load current rating of 300mA and three LDOs have load current ratings of 150mA. Single LDO operating current is less than  $80\mu\text{A}$ , making the AAT2863 ideal for battery operated applications.

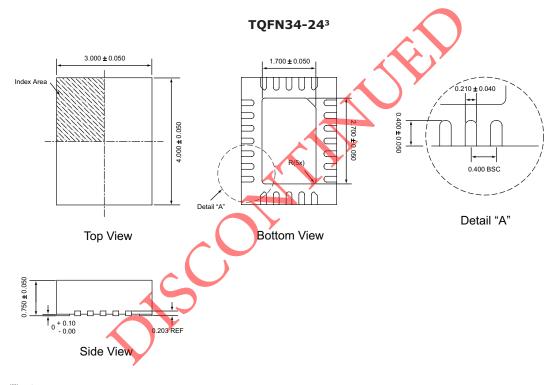

The AAT2863 is available in a Pb-free, space-saving TQFN34-24 package and operates over the -40°C to 85°C ambient temperature range.

#### **Features**

- Input Voltage Range: 2.7V to 5.5V

- Tri-Mode Charge Pump

- Drives up to Six LEDs

- Programmable Backlight Current via I<sup>2</sup>C Interface

- 30mA Maximum Current per Channel

- 60mA Maximum Current per Auxiliary Channel

- 32 Linear Current Settings

- Independent Main/Sub Settings

- Main Backlight BL1-BL6

- Main Backlight BL1-BL5 + 1 AUX

- Main Backlight BL1-BL4 + 2 Sub (default)

- Main Backlight BL1-BL4 + 2 AUX

- PWM Control

- 60Hz to 100kHz

- 600k to 1,2MHz Switching Frequency

- Automatic Soft Start

- I<sup>2</sup>C Selectable Drivers

- Four Linear Regulators

- 1 x 300mA Output LDO

- 3 x 150mA Output LDOs

- Programmable Output Voltage from 1.2V to 3.3V

- Output Auto-Discharge for Fast Shutdown

- Built-In Thermal Protection

- -40°C to 85°C Temperature Range

- TQFN34-24 Package

## **Applications**

- Camera Enabled Mobile Devices

- Digital Still Cameras

- Multimedia Mobile Phones

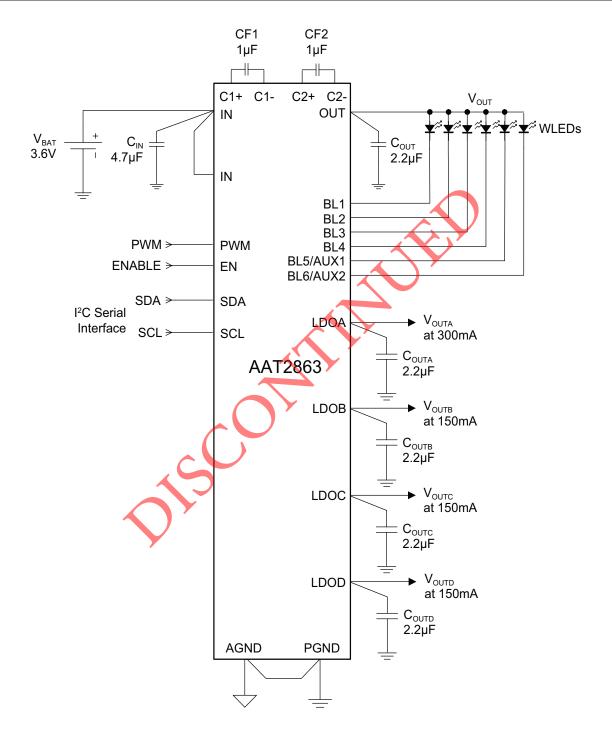

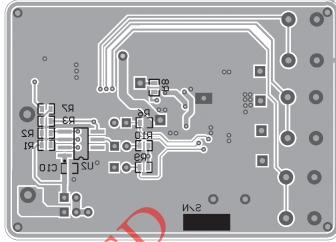

## **Typical Application Circuit**

## **Pin Descriptions**

| Pin #     | Symbol       | Function   | Description                                                                                                                                                                                                                                                                                                              |

|-----------|--------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| - r 111 # | Зуппрог      | - Tunetion | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                    |

| 1         | OUT          | 0          | Charge pump output. OUT supplies current to the backlight LEDs. Connect the backlight and flash LED anodes to OUT. Bypass OUT to PGND with a $2.2\mu F$ or larger ceramic capacitor as close to the AAT2863 as possible.                                                                                                 |

| 2         | C2+          | I          | Positive terminal of charge pump capacitor 2. Connect the $1\mu F$ charge pump capacitor 2 from C2+ to C2                                                                                                                                                                                                                |

| 3         | SDA          | I          | I <sup>2</sup> C serial data input. SDA is the data input of the I <sup>2</sup> C serial interface. Drive SDA with the I <sup>2</sup> C data.                                                                                                                                                                            |

| 4         | SCL          | I          | I <sup>2</sup> C serial clock input. SCL is the clock input of the I <sup>2</sup> C serial interface. Drive SCL with the I <sup>2</sup> C clock.                                                                                                                                                                         |

| 5         | EN           | I          | Programming enable input. When EN is strobed high, the backlight and LDO registers can be programmed via the $I^2C$ serial interface. When EN is strobed low, all backlight and LDO outputs are turned off and the backlight and LDO registers are reset to their default (POR) values and forces all LDO outputs to 0V. |

| 6         | AGND         | G          | Analog ground. Connect to PGND as close to the AAT2863 as possible                                                                                                                                                                                                                                                       |

| 7         | IN           | PI         | Input power pin for all four LDOs. Connect Pin 7 to Pin 23 with as short a PCB trace as practical.                                                                                                                                                                                                                       |

| 8         | LDOC         | 0          | LDO C 150mA regulated voltage output. Bypass LDOA to AGND with a 2.2µF or larger ceramic capacitor as close to the AAT2863 as possible.                                                                                                                                                                                  |

| 9         | LDOB         | 0          | LDO B 150mA regulated voltage output. Bypass LDOB to AGND with a 2.2µF or larger capacitor as close to the AAT2863 as possible.                                                                                                                                                                                          |

| 10        | LDOA         | 0          | LDO A 300mA regulated voltage output. Bypass LDOC to AGND with a $2.2\mu F$ or larger capacitor as close to the AAT2863 as possible.                                                                                                                                                                                     |

| 11        | LDOD         | 0          | LDO D 150mA regulated voltage output. Bypass LDOD to AGND with a 2.2µF or larger ceramic capacitor as close to the AAT2863 as possible.                                                                                                                                                                                  |

| 12        | BL1          | 0          | Backlight LED 1 current sink. BL1 controls the current through backlight LED 1. Connect the cathode of backlight LED 1 to BL1. If not used, connect BL1 to OUT.                                                                                                                                                          |

| 13        | BL2          | 0          | Backlight LED 2 current sink. BL2 controls the current through backlight LED 2. Connect the cathode of backlight LED 2 to BL2. If not used, connect BL2 to OUT.                                                                                                                                                          |

| 14        | BL3          | 0          | Backlight LED 3 current sink. BL3 controls the current through backlight LED 3. Connect the cathode of backlight LED 3 to BL3. If not used, connect BL3 to OUT.                                                                                                                                                          |

| 15        | BL4          | 0          | Backlight LED 4 current sink. BL4 controls the current through backlight LED 4. Connect the cathode of backlight LED 4 to BL4. If not used, connect BL4 to OUT.                                                                                                                                                          |

| 16        | BL6/<br>AUX2 | 0          | Backlight or auxiliary LED 6 current sink. BL6 controls the current through backlight LED 6. Connect the cathode of backlight LED 6 to BL6. If not used, connect BL6 to OUT.                                                                                                                                             |

| 17        | BL5/<br>AUX1 | 0          | Backlight or auxiliary LED 5 current sink. BL5 controls the current through backlight LED 5. Connect the cathode of backlight LED 5 to BL5. If not used, connect BL5 to OUT.                                                                                                                                             |

| 18        | N/C          |            | No connection.                                                                                                                                                                                                                                                                                                           |

| 19        | PWM          | I          | PWM input pin. Apply a PWM signal of varying duty cycle to modulate the LED current on BL1, BL2, BL3, BL4, BL5 & BL6 (Default). PWM frequency can vary up to 100kHz. The LED current maximum will be set at the default setting if no programming is applied. If not used, connect PWM to IN.                            |

| 20        | PGND         | G          | Power ground. Connect to AGND as close to the AAT2863 as possible.                                                                                                                                                                                                                                                       |

| 21        | C2-          | I          | Negative terminal of charge pump capacitor 2.                                                                                                                                                                                                                                                                            |

| 22        | C1-          | I          | Negative terminal of charge pump capacitor 1.                                                                                                                                                                                                                                                                            |

| 23        | IN           | PI         | Power input. Connect IN to the input source voltage. Bypass IN to PGND with a $4.7\mu F$ or larger ceramic capacitor as close to the AAT2863 as possible.                                                                                                                                                                |

| 24        | C1+          | I          | Positive terminal of charge pump capacitor 1. Connect the $1\mu\text{F}$ charge pump capacitor 1 from C1+ to C1                                                                                                                                                                                                          |

| EP        |              |            | Exposed paddle (bottom) Connect to PGND/AGND as close to the AAT2863 as possible.                                                                                                                                                                                                                                        |

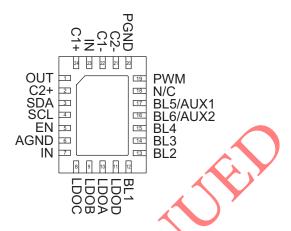

## **Pin Configurations**

# TQFN34-24 (Top View)

## **Programmable Current Sink Options**

| Main Channels | Sub Channels | Aux1 Channel | Aux2 Channel |

|---------------|--------------|--------------|--------------|

| 6             | 0            | 0            | 0            |

| 5             | 1            | 0            | 0            |

| 4*            | 2*           | 0*           | 0*           |

| 4             | 0            | 1            | 1            |

<sup>\*</sup> Default.

## **Absolute Maximum Ratings**

$T_A = 25$ °C unless otherwise noted.

| Symbol | Description                                                                  | Value                         | Units |

|--------|------------------------------------------------------------------------------|-------------------------------|-------|

|        | IN, OUT, BL1, BL2, BL3, BL4, BL5/AUX1, BL6/AUX2 Voltage to PGND and AGND     | -0.3 to 6.0                   |       |

|        | C1+, C2+ Voltage to PGND and AGND                                            | $-0.3$ to $V_{OUT} + 0.3$     | \/    |

|        | C1-, C2-, LDOA, LDOB, LDOC, LDOD, EN, PWM, SDA, SCL Voltage to PGND and AGND | -0.3 to V <sub>IN</sub> + 0.3 | V     |

|        | PGND Voltage to AGND                                                         | -0.3 to 0.3                   |       |

### Thermal Information<sup>2,3</sup>

| Symbol                 | Description                              | Value      | Units |

|------------------------|------------------------------------------|------------|-------|

| $\Theta_{\mathtt{JA}}$ | Thermal Resistance                       | 50         | °C/W  |

| P <sub>D</sub>         | Maximum Power Dissipation                | 2          | W     |

| T <sub>1</sub>         | Operating Junction Temperature Range     | -40 to 150 | ۰٫    |

| T <sub>LEAD</sub>      | Maximum Soldering Temperature (at Leads) | 300        |       |

<sup>1.</sup> Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum Rating should be applied at any one time.

Derate 20 mW/°C above 25°C ambient temperature.

<sup>3.</sup> Mounted on a FR4 circuit board.

### Electrical Characteristics<sup>1</sup>

$V_{IN}=3.6V$ ;  $C_{IN}=C_{OUT}=2.2\mu F$ ;  $C_1=C_2=1\mu F$ ;  $T_A=-40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are  $T_A=25^{\circ}C$ .

| Symbol                                                                                   | Description                                       | Conditions                                                                                | Min  | Тур  | Max  | Units |  |

|------------------------------------------------------------------------------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------|------|------|------|-------|--|

| V <sub>IN</sub>                                                                          | IN Operating Voltage Range                        |                                                                                           | 2.7  |      | 5.5  | V     |  |

|                                                                                          |                                                   | 1X Mode; $3.0 \le V_{IN} \le 5.5$ ; LDOs OFF; No Load                                     |      | 0.15 | 0.20 | mA    |  |

|                                                                                          |                                                   | $1.5 \text{X Mode}$ ; $3.0 \le V_{\text{IN}} \le 5.5$ ; LDOs OFF; Charge Pump ON; No Load |      |      | 3.0  | mA    |  |

| $I_{IN}$                                                                                 | IN Operating Current                              | 2X Mode; $3.0 \le V_{IN} \le 5.5$ ; LDOs OFF; Charge Pump ON; No Load                     |      |      | 5.0  | mA    |  |

|                                                                                          |                                                   | $2.7 \le V_{IN} \le 5.5$ ; All LDOs ON; Charge Pump OFF; No Load                          |      |      | 225  | μA    |  |

|                                                                                          |                                                   | $2.7 \le V_{IN} \le 5.5$ ; Any One LDO ON; Charge Pump OFF; No Load                       |      |      | 80   | μA    |  |

| I <sub>IN(SHDN)</sub>                                                                    | IN Shutdown Current                               | EN= GND                                                                                   |      |      | 1.0  | μA    |  |

| T <sub>SD</sub>                                                                          | Over-Temperature Shutdown<br>Threshold            |                                                                                           |      | 150  |      | °C    |  |

| T <sub>SD(HYS)</sub>                                                                     | Over-Temperature Shutdown<br>Hysteresis           |                                                                                           |      | 15   |      | °C    |  |

| Charge Pun                                                                               | np Section                                        |                                                                                           |      |      |      |       |  |

| V <sub>out</sub>                                                                         | OUT Output Voltage                                |                                                                                           |      | 5.2  |      | V     |  |

| I <sub>OUT(MAX)</sub>                                                                    | OUT Maximum Output Current                        | $V_{IN} = 3.0V, V_{OUT} = 4.0V$                                                           |      | 800  |      | mA    |  |

| V <sub>IN(TH_H, BL)</sub>                                                                | BL1-BL6 Charge Pump Mode<br>Transition Hysteresis | EN/SET = IN; V <sub>IN</sub> - V <sub>F</sub> = 1V                                        |      | 150  |      | mV    |  |

|                                                                                          |                                                   | T <sub>A</sub> = 25°C, Address 07h Data=00 (0000 0000)                                    |      | 0.6  |      |       |  |

| f f                                                                                      | Charge Pump Oscillator Frequency                  | T <sub>A</sub> = 25°C, Address 07h Data=10 (0001 0000)                                    |      | 0.8  |      | MHz   |  |

| f <sub>osc</sub>                                                                         | Charge Fullip Oscillator Frequency                | T <sub>4</sub> = 25°C, Address 07h Data=20 (0010 0000)                                    |      | 1.2  |      |       |  |

|                                                                                          |                                                   | $T_A = 25$ °C, Address 07h Data=30 (0011 0000)                                            |      | 0.6  |      |       |  |

| t <sub>CP(SS)</sub>                                                                      | Charge Pump Soft-start Time                       | T <sub>A</sub> = 25°C                                                                     |      | 100  |      | μs    |  |

| BL1-BL4, BI                                                                              | L5/AUX1, BL6/AUX2 LED Drivers                     |                                                                                           |      |      |      |       |  |

| t <sub>LED(SU)</sub>                                                                     | LED Output Current Start-up Time                  | OUT: 0V to IN                                                                             |      | 20   |      | μs    |  |

| $I_{\text{AUX}[1/2](\text{MAX})}$                                                        | AUX Maximum Current                               | Address 05h Data=E0(1110 0000)<br>Address 06h Data=E0(1110 0000)                          | 54   | 60   | 66   | mA    |  |

| I <sub>AUX[1/2](DATA13)</sub>                                                            | AUX Current                                       | Address 05h Data=AC(1010 1100)<br>Address 06h Data=AC(1010 1100)                          |      | 18.4 |      | mA    |  |

| $\begin{array}{c} \Delta I_{\text{AUX}[1/2]/} \\ I_{\text{AUX}(\text{AVG})} \end{array}$ | AUX1/AUX2 Current Matching                        | Address 05h Data=E0(1110 0000)<br>Address 06h Data=E0(1110 0000)                          |      |      | 5    | %     |  |

| I <sub>BL_(MAX)</sub>                                                                    | BL1-BL6 Maximum Current                           | Address 03h, Data=E0 (1110 0000)                                                          | 27   | 30   | 33   | mA    |  |

| I <sub>BL_(DATA29)</sub>                                                                 | BL1-BL6 Current                                   | Address 03h, Data=FD (1111 1101)                                                          | 1.75 | 1.94 | 2.13 | mA    |  |

| $\Delta I_{PWM[BL1-BL6]}/$ $I_{PWM[BL1-BL6]}$                                            | BL1-BL6 PWM Current Accuracy                      | Duty Cycle = 10%, $F_{PWM}$ = 10kHz, $V_{IN}$ - $V_F$ = 1.5V                              |      | 2.5  |      | %     |  |

| V <sub>BL_(TH)</sub>                                                                     | BL1-BL6 Charge Pump Transition<br>Threshold       | Address 03h, Data=E0 (1110 0000)                                                          |      | 180  |      | mV    |  |

<sup>1.</sup> The AAT2863 is guaranteed to meet performance specifications over the -40°C to +85°C operating temperature range and is assured by design, characterization, and correlation with statistical process controls.

Current matching is defined as the deviation of any sink current from the average of all active channels.

<sup>3.</sup>  $V_{DO[A/B/C/D]}$  is defined as  $V_{IN}$  – LDO[A/B/C/D] when LDO[A/B/C/D] is 98% of nominal.

## **Electrical Characteristics (continued)**<sup>1</sup>

$V_{IN}=3.6V$ ;  $C_{IN}=C_{OUT}=2.2\mu F$ ;  $C_1=C_2=1\mu F$ ;  $T_A=-40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are  $T_A=25^{\circ}C$ .

| Symbol                                     | Description                                            | Conditions                                                       | Min  | Тур  | Max | Units |

|--------------------------------------------|--------------------------------------------------------|------------------------------------------------------------------|------|------|-----|-------|

| Linear Regu                                | lators                                                 |                                                                  |      |      |     |       |

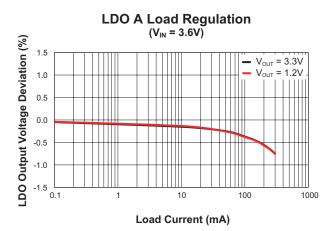

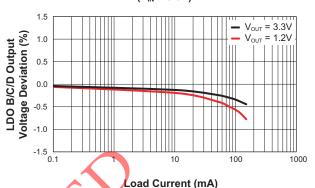

| $\Delta V_{OUT[A/B/C,D]}$                  | LDOA, LDOB, LDOC, LDOD Output                          | $I_{OUT} = 1$ mA to 150mA; $T_A = 25$ °C                         | -1.5 |      | 1.5 | %     |

| $V_{OUT[A/B/C,D]}$                         | Voltage Tolerance                                      | $I_{OUT} = 1$ mA to 150mA; $T_A = -40$ °C to $+85$ °C            | -3.0 |      | 3.0 | %     |

| $I_{OUT[A](MAX)}$                          | LDOA Maximum Load Current                              |                                                                  | 300  |      |     | mA    |

| $V_{OUT[A](DO)}$                           | LDOA Dropout Voltage <sup>3</sup>                      | $V_{OUT[A/B/C/D]} \ge 3.0V; I_{OUT} = 300mA$                     |      | 60   | 150 | mV    |

| $I_{\text{OUT}[\text{B/C,D}](\text{MAX})}$ | LDOB, LDOC, LDOD Maximum Load<br>Current               |                                                                  | 150  |      |     | mA    |

| $V_{OUT[B/C,D](DO)}$                       | LDOB, LDOC, LDOD Dropout Voltage <sup>3</sup>          | $V_{OUT[A/B/C/D]} \ge 3.0V; I_{OUT} = 150mA$                     |      | 60   | 150 | mV    |

| $\Delta V_{OUT} / V_{OUT} * \Delta V_{IN}$ | Line Regulation                                        | $V_{IN} = (V_{OUT[A/B/C/D]} + 1V)$ to 5V                         |      | 0.09 |     | %/V   |

| PSRR <sub>[A/B/C,D]</sub>                  | LDOA, LDOB, LDOC, LDOD Power<br>Supply Rejection Ratio | I <sub>OUT[A/B/C/D]</sub> = 10mA, 1kHz                           |      | 50   |     | dB    |

| R <sub>OUT_(DCHG)</sub>                    | LDOA, LDOB, LDOC, LDOD Auto-<br>Discharge Resistance   | Y                                                                |      | 20   |     | Ω     |

| I <sup>2</sup> C Logic, P                  | WM Input and Control Interface                         | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \                            |      |      |     |       |

| $V_{\text{IL}}$                            | SDA, SCL, PWM, EN Input Low<br>Threshold               | $2.7V \le V_{IN} \le 5.5V$                                       |      |      | 0.4 | V     |

| $V_{\mathrm{IH}}$                          | SDA, SCL, PWM, EN Input High<br>Threshold              | $2.7V \leq V_{IN} \leq 5.5V$                                     | 1.4  |      |     | V     |

| $V_{OL}$                                   | SDA Output Low Voltage                                 | $I_{PULLUP} = 3mA$                                               |      |      | 0.4 | V     |

| ${ m I}_{	extsf{IN}}$                      | SDA, SCL, EN Input Leakage Current                     | $V_{SDA} = V_{SCL} = V_{PWM} = V_{LED\_SEL} = V_{LDO\_SEL} = 5V$ | -1   |      | 1   | μΑ    |

| $f_{PWM}$                                  | PWM input Frequency Range                              |                                                                  | 0.6  |      | 100 | kHz   |

| $f_{SCL}$                                  | SCL Clock Frequency                                    |                                                                  | 0    |      | 400 | kHz   |

| $t_{LOW}$                                  | SCL Clock Low Period                                   |                                                                  | 1.3  |      |     | μs    |

| $t_{HIGH}$                                 | SCL Clock High Period                                  |                                                                  | 0.6  |      |     | μs    |

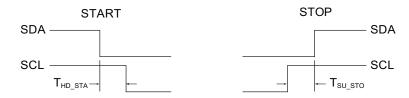

| t <sub>HD_STA</sub>                        | Hold Time START Condition                              |                                                                  | 0.6  |      |     | μs    |

| t <sub>su_sta</sub>                        | Setup Time for Repeat START                            |                                                                  | 0.6  |      |     | μs    |

| $t_{SU\_DAT}$                              | SDA Data Setup Time                                    |                                                                  | 100  |      |     | ns    |

| $t_{HD\_DAT}$                              | SDA Data HOLD Time                                     |                                                                  | 0    |      | 0.9 | μs    |

| t <sub>su_sto</sub>                        | Setup Time for STOP Condition                          |                                                                  | 0.6  |      |     | μs    |

| t <sub>BUF</sub>                           | Bus Free Time Between STOP and START Conditions        |                                                                  | 1.3  |      |     | μs    |

<sup>1.</sup> The AAT2863 is guaranteed to meet performance specifications over the -40°C to +85°C operating temperature range and is assured by design, characterization, and correlation with statistical process controls.

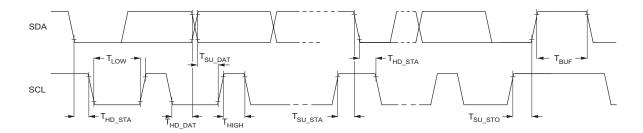

## I<sup>2</sup>C Interface Timing Details

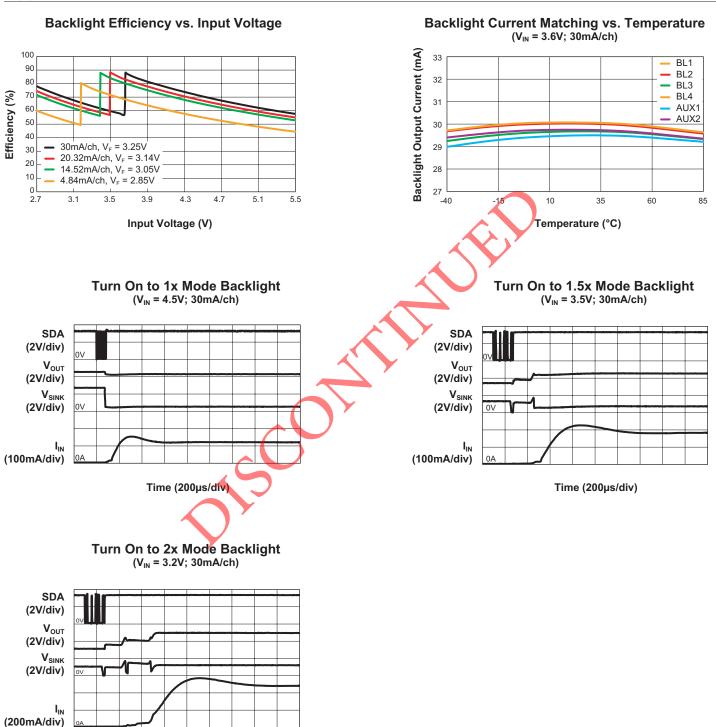

## **Typical Characteristics**

Time (200µs/div)

## **Typical Characteristics**

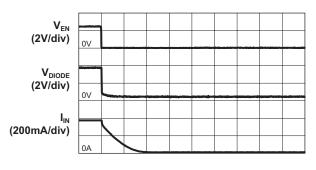

#### Turn Off from 1.5x Mode Backlight $(V_{IN} = 3.5V; 30mA/ch)$

Time (200µs/div)

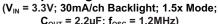

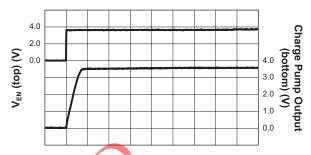

#### **Operating Characteristic**

Time (500ns/div)

## LDO A Output Voltage vs. Temperature

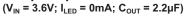

## **Charge Pump Output Turn On Characteristic**

Time (50µs/div)

#### **Operating Characteristic**

(V<sub>IN</sub> = 3.0V; 30mA/ch Backlight; 2x Mode;

Time (500ns/div)

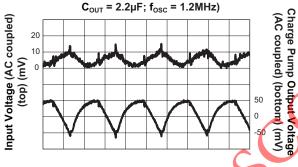

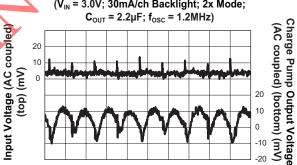

#### LDO B/C/D Output Voltage vs. Temperature $(V_{IN} = 3.6V; I_{LDO} = 0mA)$

Temperature (°C)

## **Typical Characteristics**

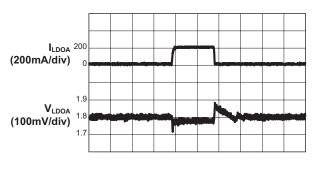

# LDO A Load Transient Response ( $I_{LDO} = 10$ mA to 200mA; $V_{IN} = 3.6V$ ; $V_{OUT} = 1.8V$ ; $C_{LDO} = 2.2\mu$ F)

Time (10µs/div)

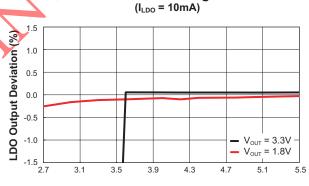

# LDO B/C/D Load Regulation (V<sub>IN</sub> = 3.6V)

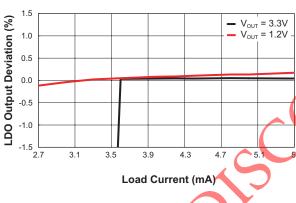

### LDO B/C/D Line Regulation

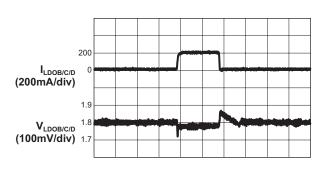

LDO B/C/D Load Transient Response ( $I_{LDO}$  = 10mA to 200mA;  $V_{IN}$  = 3.6V;  $V_{OUT}$  = 1.8V;  $C_{LDO}$  = 2.2 $\mu$ F)

Load Current (mA)

Time (20µs/div)

### **Typical Characteristics**

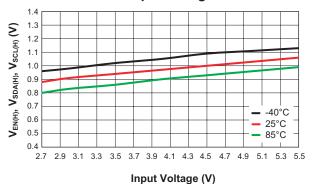

# EN, SDA, SCL Input High Threshold Voltage vs. Input Voltage

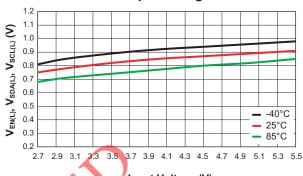

# EN, SDA, SCL Input Low Threshold Voltage vs. Input Voltage

Input Voltage (V)

## LDO A Dropout Characteristics

LDO A Dropout Characteristics

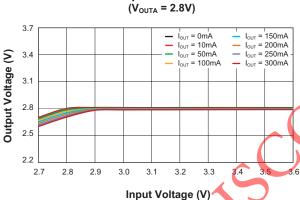

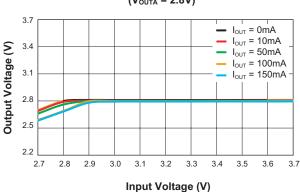

#### LDO B/C/D Dropout Characteristics (VoutA = 2.8V)

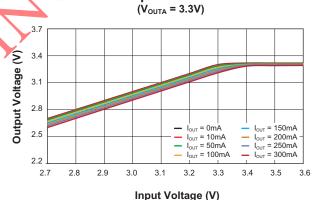

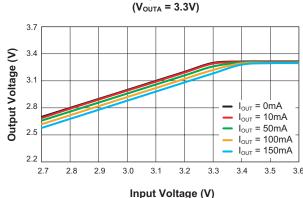

### LDO B/C/D Dropout Characteristics

## **Functional Block Diagram**

## **Functional Description**

The AAT2863 is a highly integrated white LED backlight driver with four LDO regulators intended for applications in portable products such as cell phone handsets. A multimode  $1 \times / 1.5 \times / 2 \times 1.5 \times 1.5$

and produce regulated output voltages between 1.2V and 3.3V. Control of the LEDs and the LDO output voltages is through an industry standard  $\rm I^2C$  serial interface for easy programming and system control.

#### **LED Drivers**

The AAT2863 drives up to six backlight LEDs up to 30mA each. The LEDs are driven from a multimode fractional charge pump to insure that constant current is maintained for all possible LED forward voltage over the

entire battery voltage range. The charge pump automatically switches from 1x, to 1.5x, to 2x modes and back to maintain the LED current while minimizing power loss for high efficiency. The charge pump operates at the high 1MHz switching frequency allowing the use of small  $1\mu F$  ceramic capacitors.

Depending on the battery voltage and LED forward voltage, the charge pump drives the LEDs directly from the input voltage (1x or bypass mode) or steps up the input voltage by a factor of 1.5 (1.5x mode) or 2 (2x mode). The charge pump requires only two tiny 2.2µF ceramic capacitors, making a more compact solution than an inductor-based step-up converter solution. Each individual LED is driven by a current sink to GND, allowing individual current control with high accuracy over a wide range of input voltages and LED forward voltages while maintaining high efficiency.

The charge pump is controlled by the voltage across the LED current sinks. When any one of the active backlight current sink voltages drops below 150mV, the charge pump will switch to the next higher mode (from 1x to 1.5x or from 1.5x to 2x mode) to maintain sufficient LED voltage for constant LED current. The AAT2863 continuously monitors the LED forward voltages and uses the input voltage to determine when to reduce the charge pump mode for better efficiency. There is also a 500mV mode-transition hysteresis that prevents the charge pump from oscillating between modes.

#### **LED Current Control**

LED backlight current is programmed and controlled through the  $I^2C$  serial interface as is the fade in/out function. The constant current sinks can be set between 0.5 and 30mA in approximate 1mA steps. Refer to the constant current sink  $I^2C$  serial interface programming table for detailed programmable current levels.

#### **PWM Controlled Dimming**

As an alternative to digital dimming via the  $I^2C$  interface, the AAT2863 also provides an additional PWM dimming input pin, which allows the user to control BL1-BL6 or the main BL1-BL4 and sub BL5-BL6 independently. The PWM signal will modulate the LED current set by the  $I^2C$  interface programming, making the AAT2863 compatible with various content adjusted backlight control (CABC)

and ambient light sensor (ALS) auxiliary dimming control systems. The useable input PWM frequencies frequency range for this device is 600Hz to 100kHz. The constant current sinks are proportional to the duty cycle of the PWM signal.

#### Fade In/Fade Out Function

An LED current sink fade in/fade out function is provided for smooth turn on and turn off dimming of the backlight LEDs. This function is enabled and disabled through the  $I^2C$  interface. Additionally, the LED Fade function can be applied to the main, sub or both backlights. There are four user selectable fade in/out times available.

#### LDO Regulators

The AAT2863 includes four low dropout (LDO) linear regulators. LDO regulator A has a 300mA output current capability and LDO regulators B, C and D can provide up to 150mA of load current. These regulators are powered from the battery and produce a fixed output voltages set through the I<sup>2</sup>C serial interface. The output voltage of any LDO regulator can be independently set to one of 16 output voltages between 1.2V and 3.3V. The LDO regulators can also be turned on/off through the I<sup>2</sup>C serial interface.

The LDO regulators require only a small  $2.2\mu F$  ceramic output capacitor for stability. If improved load transient response is required, larger-valued capacitors can be used without stability degradation.

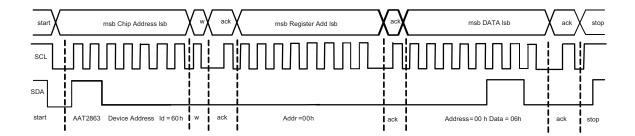

#### I<sup>2</sup>C Serial Interface

The AAT2863 uses an  $I^2C$  serial interface to set the LED currents, the LDO on/off and output voltage, as well as other housekeeping functions. The  $I^2C$  interface takes input from a master device while the AAT2863 acts as a target to the master.

The I<sup>2</sup>C protocol uses two open-drain inputs; SDA (serial data line) and SCL (serial clock line). Both inputs require an external pull up resistor, typically to the input voltage. The I<sup>2</sup>C protocol is bidirectional and allows target devices and masters to both read and write to the bus. The AAT2863 only supports the write protocol and therefore the Read/Write bit must always be set to "0". Figure 1 shows the typical transmission protocol.

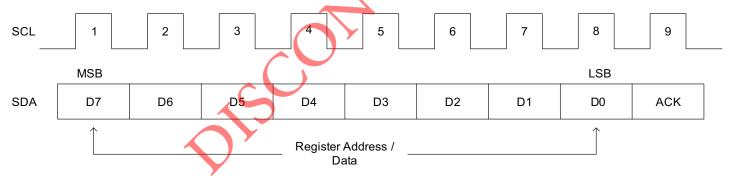

Figure 1: Typical I<sup>2</sup>C Timing Diagram.

#### I<sup>2</sup>C Serial Interface Protocol

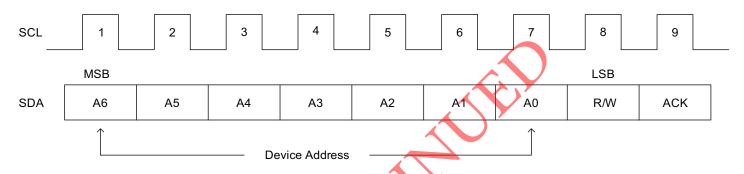

The I<sup>2</sup>C serial interface protocol is shown in Figure 1. Devices on the bus can be either master or target devices. Both master and target devices can both send and receive data over the bus, with the difference being that the master device controls all communication on the bus. The AAT2863 acts as a target device on the bus and is only capable of receiving data and does not transmit data over the bus.

The I<sup>2</sup>C communications begins by the master making a START condition. Next the master transmits the 7-bit device address and a Read/Write bit. Each target device on the bus has a unique address. The AAT2863 device address is 60h.

If the address transmitted by the master matches the device address, the target device transmits an Acknowledge (ACK) signal to indicate that it is ready to receive data. Since the AAT2863 only reads from the master, the Read/Write bit must be set to "0". Next, the master transmits the 8-bit register address, and the target device transmits an ACK to indicate that it received the register address. Next, the master transmits the 8-bit data word, and again the target device transmits an ACK indicating that it received the data. This process continues until the master is finished writing to the target device at which time the master generates a STOP condition.

#### START and STOP Conditions

START and STOP conditions are always generated by the master. Prior to initiating a START, both the SDA and SCL pin are inactive and are pulled high through external pullup resistors. As shown in Figure 1, a START condition is when the master pulls the SDA line low and, after the start condition hold time ( $t_{\text{HT\_STA}}$ ), the master strobes the SCL line low. A START condition acts as a signal to devices on the bus that the device producing the START condition is active and will be communicating on the bus.

A STOP condition, as shown in Figure 1, is when SCL changes from low to high followed after the STOP condition setup time ( $t_{SU\_STO}$ ), by an SDA low-to-high transition. The master does not issue an ACK and releases SCL and SDA.

#### **Transferring Data**

Addresses and data are sent with the most significant bit first transmitted and the least significant bit transmitted last. After each address or data transmission, the target device transmits an ACK signal to indicate that it has received the transmission. The ACK signal is generated by the target after the master releases the SDA data line by driving SDA low.

Figure 2: I<sup>2</sup>C STOP and START Conditions;

START: A High "1" to Low "0" Transition on the SDA Line While SCL is High "1" STOP: A Low "0" to High "1" Transition on the SDA Line While SCL is High "1".

Figure 3: I<sup>2</sup>C Address Bit Map; 7-bit Slave Address (A6-A0), 1-bit Read/Write (R/W), 1-bit Acknowledge (ACK).

Figure 4: I<sup>2</sup>C Register Address and Data Bit Map; 8-bit Data (D7-D0), 1-bit Acknowledge (ACK).

### **Application Information**

#### I<sup>2</sup>C Serial Programmed Registers

The AAT2863's  $I^2C$  programming registers are listed in Table 1. There are eight registers: five for the backlight LED control, and three to control the four LDO regulators.

All backlight channels can be easily configured in many different ways through the  $I^2C$  inerface. The default assignment for the drivers is four backlight for main, two backlight for sub, and two extra that can be applied to main, sub, or auxiliary. All eight backlights can be driven to the same current level by writting the MEQS = 1 option in REG3. The MAIN and SUB backlights can be programmed independently to one of 32 levels described in Table 2.

#### **Backlight Control Registers**

The AAT2863 has five backlight registers:

- REG3 (I<sup>2</sup>C address 03h) controls the MAIN backlight.

- REG4 (I<sup>2</sup>C address 04h) controls the SUB backlight.

- REG5 (I<sup>2</sup>C address 05h) controls the auxiliary AUX1 backlight.

- REG6 (I<sup>2</sup>C address 06h) controls the auxiliary AUX2 backlight.

- REG7 (I<sup>2</sup>C address 07h) controls the MAIN, SUB fade in/out function.

Table 3 describes the floor current per channel for the fade-in and fade-out functions. In fade-out sequence floor will be the final current that will continue to be present until the Main, Sub or Aux1,2 channels are disabled by writing MAIN\_ON=0 to REG3, SUB\_ON=0 to REG4, A1\_ON=0 to REG5, and/or A2\_ON=0 to REG6. In fade-in sequence floor is the direct current all channels will be turned on by writing MAIN\_ON=1 to REG3, SUB\_ON=1 to REG4, A1\_ON=1 to REG5, and/or A2\_ON=1 to REG6.

| Regis  | ter         |                                     |         |                      |              | 7            |           |          |          |          |

|--------|-------------|-------------------------------------|---------|----------------------|--------------|--------------|-----------|----------|----------|----------|

| Number | Hex<br>Code | Function                            | Bit7    | Bit6                 | Bit5         | Bit4         | Bit3      | Bit2     | Bit1     | Bit0     |

| REG0   | 00h         | LDO A & B Output<br>Voltage Control | LDOA[3] | LDOA[2]              | LDOA[1]      | LDOA[0]      | LDOB[3]   | LDOB[2]  | LDOB[1]  | LDOB[0]  |

| REG1   | 01h         | LDO C & D Output<br>Voltage Control | LDOC[3] | LDOC[2]              | LDOC[1]      | LDOC[0]      | LDOD[3]   | LDOD[2]  | LDOD[1]  | LDOD[0]  |

| REG2   | 02h         | LDO EN CONTROL                      | X       | Х                    | X            | X            | ENLDO_D   | ENLDO_C  | ENLDO_B  | ENLDO_A  |

| REG3   | 03h         | Backlight Current<br>Control MAIN   | MEQS    | DISABLE<br>FADE_MAIN | MAIN_ON      | BLM[4]       | BLM[3]    | BLM[2]   | BLM[1]   | BLM[0]   |

| REG4   | 04h         | Backlight Current<br>Control SUB    | X       | DISABLE<br>FADE_SUB  | SUB_ON       | BLS[4]       | BLS[3]    | BLS[2]   | BLS[1]   | BLS[0]   |

| REG5   | 05h         | Backlight Current<br>Control AUX1   | AUX1[1] | AUX1[0]              | A1_ON        | BLA1[4]      | BLA1[3]   | BLA1[2]  | BLA1[1]  | BLA1[0]  |

| REG6   | 06h         | Backlight Current<br>Control AUX2   | AUX2[2] | AUX2[0]              | A2_ON        | BLA2[4]      | BLA2[3]   | BLA2[2]  | BLA2[1]  | BLA2[0]  |

| REG7   | 07h         | Backlight Fade<br>Control           | Х       | Х                    | FADE_TIME[1] | FADE_TIME[0] | FADE_MAIN | FADE_SUB | FLOOR[1] | FLOOR[0] |

Table 1: AAT2863 Configuration/Control Register Allocation ("X" = Reserved).

| Bit4                                   | Bit3                                   | Bit2                                   | Bit1                                   | Bit0                                   | LED Current (mA)             |

|----------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|------------------------------|

| BLM[4]<br>BLS[4]<br>BLA1[4]<br>BLA2[4] | BLM[3]<br>BLM[3]<br>BLA1[3]<br>BLA2[3] | BLM[2]<br>BLS[2]<br>BLA1[2]<br>BLA2[2] | BLM[1]<br>BLS[1]<br>BLA1[1]<br>BLA2[1] | BLM[0]<br>BLS[0]<br>BLA1[0]<br>BLA2[0] | REG3<br>REG4<br>REG5<br>REG6 |

| 0                                      | 0                                      | 0                                      | 0                                      | 0                                      | 30*                          |

| 0                                      | 0                                      | 0                                      | 0                                      | 1                                      | 29.03                        |

| 0                                      | 0                                      | 0                                      | 1                                      | 0                                      | 28.06                        |

| 0                                      | 0                                      | 0                                      | 1                                      | 1                                      | 27.10                        |

| 0                                      | 0                                      | 1                                      | 0                                      | 0                                      | 26.13                        |

| 0                                      | 0                                      | 1                                      | 0                                      | 1                                      | 25.16                        |

| 0                                      | 0                                      | 1                                      | 1                                      | 0                                      | 24.19                        |

| 0                                      | 0                                      | 1                                      | 1                                      | 1                                      | 23.23                        |

| 0                                      | 1                                      | 0                                      | 0                                      | 0                                      | 22.26                        |

| 0                                      | 1                                      | 0                                      | 0                                      | 1                                      | 21.29                        |

| 0                                      | 1                                      | 0                                      | 1                                      | 0                                      | 20.32                        |

| 0                                      | 1                                      | 0                                      | 1                                      | 1 )                                    | 19.35                        |

| 0                                      | 1                                      | 1                                      | 0                                      | 0                                      | 18.38                        |

| 0                                      | 1                                      | 1                                      | 0                                      | 1                                      | 17.42                        |

| 0                                      | 1                                      | 1                                      | 1                                      | 0                                      | 16.45                        |

| 0                                      | 1                                      | 1                                      | 1                                      | 1                                      | 15.48                        |

| 1                                      | 0                                      | 0                                      | 0                                      | 0                                      | 14.52                        |

| 1                                      | 0                                      | 0                                      | 0                                      | 1                                      | 13.55                        |

| 1                                      | 0                                      | 0                                      | 1                                      | 0                                      | 12.58                        |

| 1                                      | 0                                      | 0                                      | 1                                      | 1                                      | 11.61                        |

| 1                                      | 0                                      | 1                                      | 0                                      | 0                                      | 10.65                        |

| 1                                      | 0                                      | 1 .                                    | 0                                      | 1                                      | 9.68                         |

| 1                                      | 0                                      | 1                                      | 1                                      | 0                                      | 8.71                         |

| 1                                      | 0                                      | 1                                      | 1                                      | 1                                      | 7.74                         |

| 1                                      | 1                                      | 0                                      | 0                                      | 0                                      | 6.77                         |

| 1                                      | 1                                      | 0                                      | 0                                      | 1                                      | 5.81                         |

| 1                                      | 1                                      |                                        | 1                                      | 0                                      | 4.84                         |

| 1                                      | 1                                      | 0                                      | 1                                      | 1                                      | 3.87                         |

| 1                                      | 1                                      | 1                                      | 0                                      | 0                                      | 2.9                          |

| 1                                      | 1                                      | 1                                      | 0                                      | 1                                      | 1.94                         |

| 1                                      | 1                                      | 1                                      | 1                                      | 0                                      | 0.97                         |

| 1                                      | 1                                      | 1                                      | 1                                      | 1                                      | 0.48                         |

Table 2: Main/Sub/Aux Backlight LED Current - BLM/BLS/BLA [4:0].

| Bit1    | Bit 0   | Fade Out Current Level (mA) |

|---------|---------|-----------------------------|

| FLOOR 1 | FLOOR 0 | REG7                        |

| 0*      | 0*      | 0.48*                       |

| 0       | 1       | 0.97                        |

| 1       | 0       | 1.94                        |

| 1       | 1       | 2.90                        |

Table 3: Main/Sub LED Current Fade OUT Level Control.

<sup>\*</sup> Denotes default (power-on-reset) value.

Table 4 describes the final current per channel after the fade out sequence that will continue to be present until the MAN, SUB or AUX1,2 channels are disabled by writing to Bit 5=1 to REG3, REG4, REG5 or REG6. Fade OUT can be initiated only after Bit2 or Bit3 of REG7 have been programmed for fade in sequence first by writing FADE\_MAIN = 1 or FADE SUB = 1.

| Bit3      | Bit 2    | Fade IN / OUT Control<br>REG7 |          |  |

|-----------|----------|-------------------------------|----------|--|

| FADE_MAIN | FADE_SUB | MAIN                          | SUB      |  |

| 0*        | 0*       | Fade OUT                      | Fade OUT |  |

| 0         | 1        | Fade OUT                      | Fade IN  |  |

| 1         | 0        | Fade IN                       | Fade OUT |  |

| 1         | 1        | Fade IN                       | Fade IN  |  |

Table 4: Main/Sub LED Current Fade IN/OUT Control.

Table 5 describes Data Bit4 and Data Bit5 of REG7 control the duration of the fade-in/out function. The default timing is 850ms with options for 650ms and 425ms according to Table 5. The charge pump oscillator frequency is related to the fade-in/out timing as follows:

For the 850ms fade-in/out timer, typical  $f_{\rm osc}=600 kHz$  For the 650ms fade-in/out timer, typical  $f_{\rm osc}=800 kHz$  For the 425ms fade-in/out timer, typical  $f_{\rm osc}=1.2 kHz$

| Bit5         | Bit 4        | Fade IN and OUT |

|--------------|--------------|-----------------|

| FADE_TIME[1] | FADE_TIME[0] | Timing (ms)     |

| 0*           | 0*           | 850*            |

| 0            | 1            | 650             |

| 1            | 0            | 425             |

| 1            | 1            | 850             |

Table 5: Main/Sub LED current Fade IN /OUT Timing Selection.

Data Bit5 of REG3, REG4, REG4 and REG5 controls the turn on/off of the MAIN, SUB, AUX1 and AUX2 channels.

| Bit 5   | Backlight Channel ON/OFF |

|---------|--------------------------|

| MAIN_ON | REG3                     |

| SUB_ON  | REG4                     |

| AUX1_ON | REG5                     |

| AUX1_ON | REG6                     |

| 0*      | OFF                      |

| 1       | ON                       |

Table 6: Main/Sub/Aux LED Current ON/OFF Control.

Data Bit6 of REG3 and REG4 enable the fade control of the MAIN and SUB channels. Fade function can be explicitly disabled by writing DISABLE FADE\_MAIN = 1 and DISABLE FADE\_SUB = 1.

|   | Bit 6                                 | Backlight Channel Fade<br>Enable/Disable |

|---|---------------------------------------|------------------------------------------|

| 1 | DISABLE FADE_MAIN<br>DISABLE FADE_SUB | REG3<br>REG4                             |

|   | 0*                                    | Enable                                   |

|   | 1                                     | Disable                                  |

Table 7: Main/Sub Current Fade ON/OFF Control.

Data Bit7 of REG3 programs all SUB channels as MAIN backlight. In this case if the MAIN fade function is enabled all MAIN and SUB channels will be faded simultaneously.

| Bit 7 | MAIN Equal SUB |  |

|-------|----------------|--|

| MEQS  | REG3           |  |

| 0*    | False          |  |

| 1     | True           |  |

Table 8: Main/Sub Current Fade ON/OFF Control.

<sup>\*</sup>Denotes default (power-on-reset) value.

#### **Examples of Fade-Out Programming**

#### Main Only (Sub is OFF):

Address 03h, Data 40: Disable fade

Address 07h, Data 08: Fade-in is programmed

Address 03h, Data 6F: Turn on directly to 15.48mA/ch

Address 03h, Data 20: Re-enable fade

Address 07h, Data 00: Fade-out to 0.48mA/ch

#### Sub Only (Main is OFF):

Address 04h, Data 40: Disable fade

Address 07h, Data 04: Fade-in is programmed

Address 04h, Data 6F: Turn on directly to 15.48mA/ch

Address 04h, Data 2F: Enable fade

Address 07h, Data 02: Fade-out to 1.94mA/ch

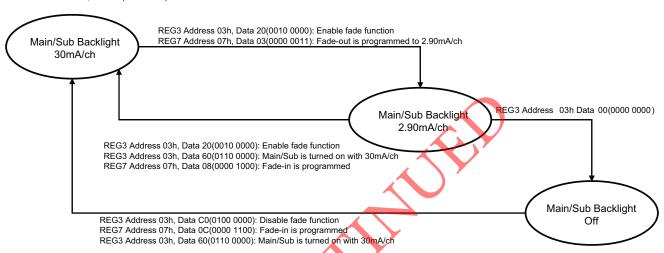

#### Main and Sub (as shown in Figure 5):

Address 03h, Data CO: Disable fade

Address 07h, Data 0C: Fade-in is programmed

Address 03h, Data 60: Turn on directly to 30mA/ch

Address 03h, Data 20: Enable fade

Address 07h, Data 03: Fade-out to 2.90mA/ch

#### **Examples of Fade-In/Out Programming**

#### Main Only (Sub is OFF):

Address 03h, Data 20: Main backlight is turned on with 0.48mA/ch

Address 07h, Data 08: Fade-in to 30mA/ch

Address 07h, Data 03: Fade-out to 2.90mA/ch

#### Sub Only (Main is OFF):

Address 07h, Data 02: Fade-in is programmed to 1.94mA/ch

Address 04h, Data 2E: Sub backlight is turned on with 1.94mA/ch

Address 07h, Data 04: Fade-in to 16.45mA/ch

Address 07h, Data 02: Fade-out to 1.94mA/ch

#### Main and Sub (as shown in Figure 6):

Address 07h, Data 01: Fade-in is programmed to 0.97mA/ch

Address 03h, Data AA: Main and Sub backlight is turned on with 0.97mA/ch

Address 07h, Data 0C: Fade-in to 20.32mA/ch

Address 07h, Data 01: Fade-out to 0.97mA/ch

# Main and Sub Fade Out Only Max. 30mA/ch to 2.90mA/ch

AAT2863 Chip Address 60h REG3 Address 03h, Data C0(0100 0000): Disable fade function REG7 Address 07h, Data 0C(0000 1100): Fade-in is programmed REG3 Address 03h, Data 60(0110 0000): Main/Sub is turned on with 30mA/ch

I2C Sequence:

Figure 5: Example of AAT2863 Fade Out Programming.

### Main and Sub Fade In/Out Max. 20.32mA/ch to 0.97mA/ch I<sup>2</sup>C Sequence: AAT2863 Chip Address 60h REG7 Address 07h, Data 01(0000 0001): Fade-in is programmed as 0.97mA/ch REG3 Address 03h, Data AA(1010 1010): Main/Sub backlight is turned on with 0.97mA/ch REG7 Address 07h, Data 0C(0000 1100): Fade-in programmed to 20.32mA/ch REG7 Address 07h, Data 01(0000 0001): Fade-out is programmed to 0.97mA/ch Main/Sub Backlight 20.32mA/ch REG7 Address 07h, Data 0C(0000 1100): REG3 Address 03h Data 80(1000 0000) Fade-in is programmed as 20.32mA/ch Main/Sub Backlight 0.97mA/ch REG7 Address 07h, Data 01(0000 0001): Fade-in is programmed as 0.97mA/ch REG3 Address 03h, Data AA(1010 1010): Main/Sub backlight is turned on with 0.97mA/ch REG7 Address 07h, Data 0C(0000 1100): Fade-in is programmed to 20.32mA/ch Main/Sub Backlight Off

Figure 6: Example of AAT2863 Fade In/Out Programming.

#### **LDO Control Registers**

The four LDO regulators each have three dedicated control registers:

- REG0 (I<sup>2</sup>C address 00h) and REG1 (I<sup>2</sup>C address 01h) set the output voltages of LDOA/B/C/D to one of 16 pre-set values according to Table 9 and Table 10.

- REG2 (I<sup>2</sup>C address 02h) controls turning on/off of LDOA/B/C/D regulators according to Table 11.

| Bit7               | Bit6               | Bit5               | Bit4               | LDO V <sub>OUT[A/C]</sub> (V) |

|--------------------|--------------------|--------------------|--------------------|-------------------------------|

| LDOA[3]<br>LDOC[3] | LDOA[2]<br>LDOC[2] | LDOA[1]<br>LDOC[1] | LDOA[0]<br>LDOC[0] | REG0<br>REG1                  |

| 0*                 | 0*                 | 0*                 | 0*                 | 1.2*                          |

| 0                  | 0                  | 0                  | 1                  | 1.3                           |

| 0                  | 0                  | 1                  | 0                  | 1.5                           |

| 0                  | 0                  | 1                  | 1                  | 1.6                           |

| 0                  | 1                  | 0                  | 0                  | 1.8                           |

| 0                  | 1                  | 0                  | 1                  | 2.0                           |

| 0                  | 1                  | 1                  | 0                  | 2.2                           |

| 0                  | 1                  | 1                  | 1                  | 2.5                           |

| 1                  | 0                  | 0                  | 0                  | 2.6                           |

| 1                  | 0                  | 0                  | 1                  | 2.7                           |

| 1                  | 0                  | 1                  | 0                  | 2.8                           |

| 1                  | 0                  | 1                  | 1                  | 2.9                           |

| 1                  | 1                  | 0                  | 0                  | 3.0                           |

| 1                  | 1                  | 0                  | 1                  | 3.1                           |

| 1                  | 1                  | 1                  | 0                  | 3.2                           |

| 1                  | 1                  | 1                  | 1                  | 3.3                           |

Table 9: LDOA/LDOC Output Voltage Control Data.

| Bit3               | Bit2               | Bit1               | Bit0               | LDO V <sub>OUT[B/D]</sub> (V) |

|--------------------|--------------------|--------------------|--------------------|-------------------------------|

| LDOB[3]<br>LDOD[3] | LDOB[2]<br>LDOD[2] | LDOB[1]<br>LDOD[1] | LDOB[0]<br>LDOD[0] | REGO<br>REG1                  |

| 0*                 | 0*                 | 0*                 | 0*                 | 1.2*                          |

| 0                  | 0                  | 0                  | 1                  | 1.3                           |

| 0                  | 0                  | 1                  | 0                  | 1.5                           |

| 0                  | 0                  | 1                  | 1                  | 1.6                           |

| 0                  | 1                  | 0                  | 0                  | 1.8                           |

| 0                  | 1                  | 0                  | 1                  | 2.0                           |

| 0                  | 1                  | 1                  | 0                  | 2.2                           |

| 0                  | 1                  | 1                  | 1                  | 2.5                           |

| 1                  | 0                  | 0                  | 0                  | 2.6                           |

| 1                  | 0                  | 0                  | 1                  | 2.7                           |

| 1                  | 0                  | 1                  | 0                  | 2.8                           |

| 1                  | 0                  | 1                  | 1                  | 2.9                           |

| 1                  | 1                  | 0                  | 0                  | 3.0                           |

| 1                  | 1                  | 0                  | 1                  | 3.1                           |

| 1                  | 1                  | 1                  | 0                  | 3.2                           |

| 1                  | 1                  | 1                  | 1                  | 3.3                           |

Table 10: LDOB/LDOD Output Voltage Control Data.

<sup>\*</sup>Denotes default (power-on-reset) value.

| Bit3    | Bit2    | Bit1    | Bit0    |      |      |      |      |

|---------|---------|---------|---------|------|------|------|------|

| ENLDO_D | ENLDO_C | ENLDO_B | ENLDO_A | LDOD | LDOC | LDOB | LDOA |

| 0*      | 0*      | 0*      | 0*      | OFF  | OFF  | OFF  | OFF  |

| 0       | 0       | 0       | 1       | OFF  | OFF  | OFF  | ON   |

| 0       | 0       | 1       | 0       | OFF  | OFF  | ON   | OFF  |

| 0       | 0       | 1       | 1       | OFF  | OFF  | ON   | ON   |

| 0       | 1       | 0       | 0       | OFF  | ON   | OFF  | OFF  |

| 0       | 1       | 0       | 1       | OFF  | ON   | OFF  | ON   |

| 0       | 1       | 1       | 0       | OFF  | ON   | ON   | OFF  |

| 0       | 1       | 1       | 1       | OFF  | ON   | ON   | ON   |

| 1       | 0       | 0       | 0       | ON   | OFF  | OFF  | OFF  |

| 1       | 0       | 0       | 1       | ON   | OFF  | OFF  | ON   |

| 1       | 0       | 1       | 0       | ON   | OFF  | ON   | OFF  |

| 1       | 0       | 1       | 1       | ON   | OFF  | ON   | ON   |

| 1       | 1       | 0       | 0       | ON 🗸 | ON   | OFF  | OFF  |

| 1       | 1       | 0       | 1       | ON   | ÓN   | OFF  | ON   |

| 1       | 1       | 1       | 0       | ON   | ON   | ON   | OFF  |

| 1       | 1       | 1       | 1       | ON   | ON   | ON   | ON   |

Table 11: LDOA/LDOB/LDOC/LDOD ON/OFF Control Data.

#### **Auxiliary Backlight Selection**

Each of the auxiliary drivers (AUX) can also be programmed to one of 32 levels described in Table 2. The auxiliary drivers can be driven independently, or combined with the main or sub by changing Bit6 and Bit7 in REG5 (I<sup>2</sup>C address 05h) and REG6 (I<sup>2</sup>C address 06h) according to Table 12. The auxiliary drivers can also be set to operate at twice their programmed current if Bit6=1 and Bit7=1 in REG5 and REG6.

| Bit7               | Bit6               | Auxiliary Channel Assignment |

|--------------------|--------------------|------------------------------|

| AUX1[1]<br>AUX2[1] | AUX1[0]<br>AUX2[0] | REG5<br>REG6                 |

| 0*                 | 0*                 | SUB                          |

| 0                  | 1                  | MAIN                         |

| 1                  | 0                  | AUX                          |

| 1                  | 1                  | AUX * 2                      |

Table 12: Auxiliary Channels Assignment.

#### **LED Selection**

The AAT2863 is specifically intended for driving white LEDs. However, the device design will allow the AAT2863 to drive most types of LEDs with forward voltage specifications ranging from 2.0V to 4.7V. LED applications may include mixed arrangements for display backlighting, color (RGB) LEDs, infrared (IR) diodes and any other load needing a constant current source generated from a varying input voltage. Since the D1 to D8 constant current sinks are matched with negligible voltage dependence, the constant current channels will be matched regardless of the specific LED forward voltage ( $V_{\rm F}$ ) levels.

The *low-dropout* current sinks in the AAT2863 maximize performance and make it capable of driving LEDs with high forward voltages. Multiple channels can be combined to obtain a higher LED drive current without complication.

<sup>\*</sup>Denotes default (power-on-reset) value.

#### **Device Switching Noise Performance**

The AAT2863 operates at a fixed frequency of approximately 1MHz to control noise and limit harmonics that can interfere with the RF operation of cellular telephone handsets or other communication devices. Back-injected noise appearing on the input pin of the charge pump is 20mV peak-to-peak, typically ten times less than inductor-based DC/DC boost converter white LED backlight solutions. The AAT2863 soft-start feature prevents noise transient effects associated with in-rush currents during the start up of the charge pump circuit.

#### **Power Efficiency and Device Evaluation**

Charge-pump efficiency discussion in the following sections accounts only for the efficiency of the charge pump section itself. Due to the unique circuit architecture and design of the AAT2863, it is very difficult to measure efficiency in terms of a percent value comparing input power over output power.

Since the AAT2863 outputs are pure constant current sinks and typically drive individual loads, it is difficult to measure the output voltage for a given output (BL1 to BL8) to derive an overall output power measurement. For any given application, white LED forward voltage levels can differ, yet the output drive current will be maintained as a constant.

This makes quantifying output power a difficult task when taken in the context of comparing to other white LED driver circuit topologies. A better way to quantify total device efficiency is to observe the total input power to the device for a given LED current drive level. The best White LED driver for a given application should be based on trade-offs of size, external component count, reliability, operating range and total energy usage...Not just "% efficiency".

The AAT2863 efficiency may be quantified under very specific conditions and is dependent upon the input voltage versus the output voltage seen across the loads applied to outputs D1 through D8 for a given constant current setting. Depending on the combination of  $V_{\rm IN}$  and voltages sensed at the current sinks, the device will operate in load switch mode. When any one of the voltages sensed at the current sinks nears dropout the device will operate in 1.5x or 2x charge pump mode. Each of these modes will yield different efficiency values. One should refer to the following two sections for explanations for each operational mode.

#### 1x Mode Efficiency

The AAT2863's 1x mode is operational at all times and functions alone to enhance device power conversion efficiency when  $V_{\text{IN}}$  is greater then the voltage across the load. When in 1x mode, the voltage conversion efficiency is defined as output power divided by input power:

$$\eta = \frac{P_{OUT}}{P_{IN}}$$

The expression to define the ideal efficiency  $(\eta)$  can be rewritten as:

$$\eta = \frac{P_{OUT}}{P_{IN}} = \frac{V_{OUT} \cdot I_{OUT}}{V_{IN} \cdot I_{OUT}} = \frac{V_{OUT}}{V_{IN}}$$

-or-

$$\eta(\%) = 100 \left(\frac{V_{OUT}}{V_{IN}}\right)$$

#### 1.5x/2x Charge Pump Mode Efficiency

The AAT2863 contains a fractional charge pump which will boost the input supply voltage in the event where  $V_{\text{IN}}$  is less then the voltage required to supply the output. The efficiency  $(\eta)$  can be simply defined as a linear voltage regulator with an effective output voltage that is equal to one and a half or two times the input voltage. Efficiency  $(\eta)$  for an ideal 1.5x charge pump can typically be expressed as the output power divided by the input power.

$$\eta = \frac{P_{OUT}}{P_{IN}}$$

In addition, with an ideal 1.5x charge pump, the output current may be expressed as 2/3 of the input current. The expression to define the ideal efficiency ( $\eta$ ) can be rewritten as:

$$\eta = \frac{P_{\text{OUT}}}{P_{\text{IN}}} = \frac{V_{\text{OUT}} \cdot I_{\text{OUT}}}{V_{\text{IN}} \cdot 1.5 I_{\text{OUT}}} = \ \frac{V_{\text{OUT}}}{1.5 V_{\text{IN}}}$$

$$\eta(\%) = 100 \left( \frac{V_{OUT}}{1.5 V_{IN}} \right)$$

For a charge pump with an output of 5V and a nominal input of 3.5V, the theoretical efficiency is 95%. Due to internal switching losses and IC quiescent current consumption, the actual efficiency can be measured at 93%. These figures are in close agreement for output load conditions from 1mA to 100mA. Efficiency will decrease substantially as load current drops below 1mA or when level of  $V_{\rm IN}$  approaches  $V_{\rm OUT}$ .

The same calculations apply for 2x mode where the output current then becomes 1/2 of the input current.

#### **Capacitor Selection**

Careful selection of the four external capacitors  $C_{\text{IN}}$ , C1, C2,  $C_{\text{OUT}}$  is important because they will affect turn on time, output ripple and transient performance. Optimum performance will be obtained when low ESR (<100m $\Omega$ ) ceramic capacitors are used. In general, low ESR may be defined as less than  $100m\Omega$ . A capacitor value of  $1\mu\text{F}$  for all four capacitors is a good starting point when choosing capacitors. If the constant current sinks are only programmed for light current levels, then the capacitor size may be decreased.

#### **Capacitor Characteristics**

Ceramic composition capacitors are highly recommended over all other types of capacitors for use with the AAT2863. Ceramic capacitors offer many advantages over their tantalum and aluminum electrolytic counterparts. A ceramic capacitor typically has very low ESR, is lowest cost, has a smaller PCB footprint and is non-polarized. Low ESR ceramic capacitors help to maximize charge pump transient response. Since ceramic capacitors are non-polarized, they are not prone to incorrect connection damage.

#### **Equivalent Series Resistance (ESR)**

ESR is an important characteristic to consider when selecting a capacitor. ESR is a resistance internal to a capacitor, which is caused by the leads, internal connections, size or area, material composition and ambient temperature. Capacitor ESR is typically measured in milliohms for ceramic capacitors and can range to more than several ohms for tantalum or aluminum electrolytic capacitors.

#### **Ceramic Capacitor Materials**

Ceramic capacitors less than  $0.1\mu F$  are typically made from NPO or COG materials. NPO and COG materials typically have tight tolerance and are stable over temperature. Larger capacitor values are typically composed of X7R, X5R, Z5U or Y5V dielectric materials. Large ceramic capacitors, typically greater than  $2.2\mu F$  are often available in low cost Y5V and Z5U dielectrics, but capacitors greater than  $1\mu F$  are typically not required for AAT2863 applications.

Capacitor area is another contributor to ESR. Capacitors that are physically large will have a lower ESR when compared to an equivalent material smaller capacitor. These larger devices can improve circuit transient response when compared to an equal value capacitor in a smaller package size.

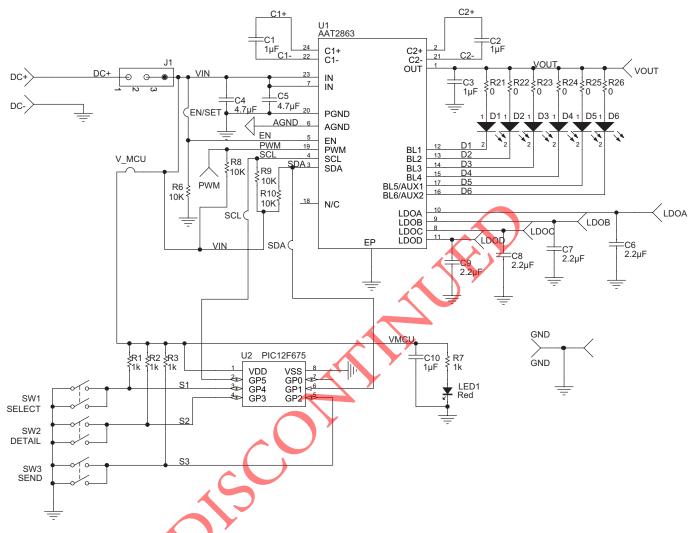

#### **Evaluation Board User Interface**

The user interface for the AAT2863 evaluation board is provided by three buttons and three connection terminals. The board is operated by supplying external power and pressing individual buttons or button combinations. Table 14 indicates the function of each button or button combination.

To power-on the evaluation board, connect a power supply or battery to the DC- and DC+ terminals. Close the board's supply connection by positioning the J1 jumper to the ON position. A red LED indicates that power is applied.

The evaluation board is made flexible so that the user can disconnect the data, clock and enable lines from the microcontroller and apply external signal sources by removing the jumpers from J2, J3 and/or J4. External enable signal must be applied to the ON pin of J4 terminal. External I<sup>2</sup>C clock SCL can be applied to J2 pin and data SDA to J3 pin.

When applying external enable signals, consideration must be given to the voltage levels. The externally applied voltages should not exceed the supply voltage that is applied to the IN pins of the device (DC+). The LDO loads can be connected directly to the evaluation board. For adequate performance, be sure to connect the load between LDOA/LDOB/LDOC/LDOD and DC- as opposed to some other GND in the system.

| Manufacturer | Part Number    | Value | Voltage | Temp. Co. | Case  |

|--------------|----------------|-------|---------|-----------|-------|

| AVX          | 0603ZD105K     | 1uF   | 10      | X5R       | 0603  |

| AVA          | 0603ZD225K     | 2.2µF | 10      | ASK       |       |

|              | C1608X5R1E105K | 1µF   | 25      |           | 0603  |

| TDK          | C1608X5R1C225K | 2.2µF | 16      | X5R       |       |

|              | C1608X5R1A475K | 4.7µF | 10      |           |       |

| Murata       | GRM188R61C105K | 1µF   | 16      | X5R       | 0.000 |

| Murata       | GRM188R61A225K | 2.2µF | 10      | ASK       | 0603  |

| Taiyo Yuden  | LMK107BJ475KA  | 4.7µF | 10      | X5R       | 0603  |

**Table 13: Surface Mount Capacitors.**

| Button(s) Pushed                                                                                                         | Description                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SW1 (LDOs)                                                                                                               | [Push/Release once] All LDOs will be turned on with default output voltage 1.2V. Every push release will increment output voltage according to datasheet table.                      |

| SW2 (Main Backlight)                                                                                                     | [Push/Release once] Turning on the Main and Sub backlight LEDs with default current 30mA per channel. Every push release will increment output voltage according to datasheet table. |

| SW3 (Sub/Aux Backlight)                                                                                                  | [Push/Release once] Turning on only the Sub/Aux backlight LEDs with default current 30mA. Every push release will increment output voltage according to datasheet table.             |

| SW1+SW2                                                                                                                  | [Push/Release once] Turning on the fade-out sequence of the backlight LEDs with default current 30mA down to 0.5mA per channel.                                                      |

| SW1+SW3 [Push/Release once] Turning on the fade-in sequence of the backlight LEDs with def 0.5mA up to 30mA per channel. |                                                                                                                                                                                      |

| SW1+SW2+SW3                                                                                                              | [Push/Release once] Reset all registers to default.                                                                                                                                  |

Table 14: AAT2863 Evaluation Board User Interface Functionality.

STSCO,

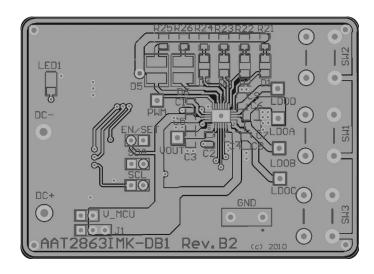

Figure 7: AAT2863 Evaluation Board Schematic.

Figure 8: AAT2863 Evaluation Board Top Side Layout.

Figure 9: AAT2863 Evaluation Board Layout Bottom Side Layout.